박사라이팅

Cache Coherence 본문

성균관대학교 조형민 교수님 "컴퓨터구조설계특론" 수업을 바탕으로 만들었습니다.

Cache Coherence는 말 그대로, Cache의 일관성을 말합니다. Multi-core 환경에서 여러 processor들이 하나의 main memory를 쓰면서 cache coherence 문제가 생깁니다. 하나의 processor가 main memory에 write하거나 그 processor의 private cache에 write하게 되면, 그와 같은 address를 가진 다른 processor의 cache도 write한 값을 가져야 합니다. 이것을 cache coherence라고 부르죠.

오늘은 가장 중요한 Cache Coherence에 대해 배워보겠습니다.

Bus Management

Bus는 공유된 wire들의 모음집과 비슷합니다. Initiator (master)가 read/write와 같은 신호를 보내면 Responder (slave)가 그 신호를 받아 data를 주고받죠. 하지만 Bus를 가지고 data를 주고 받는 것은 한번에 하나만 가능합니다. 즉 하나의 "Initiator"가 driving wires를 통해 initiate할 수 있죠.

Initiator가 bus controller에 access를 위한 request를 보내면, 정렬하여 grant를 보냅니다. Responder는 여러개가 wire에 있는 transaction을 respond할 수 있죠. responder가 bus에 있는 address를 decode해서 respond해야하는 지의 여부를 판단합니다.

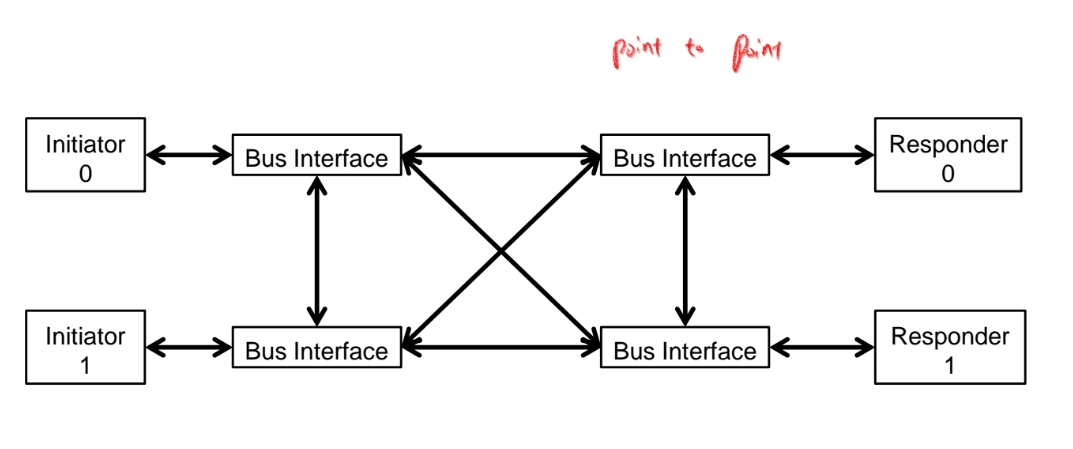

Point-to-point Buses

Initiator와 Responder가 서로 Bus interface를 사용하여 의사소통하는 방식은 여러 가지가 있지만 위가 대표적입니다.

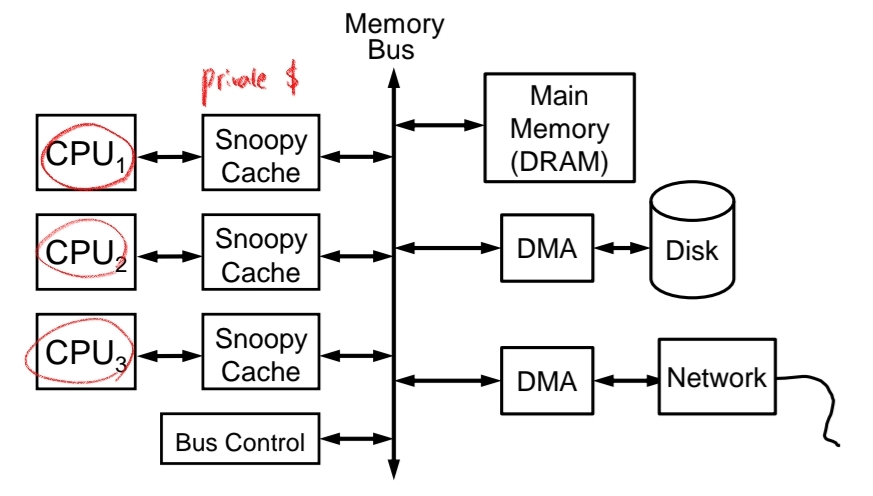

Shared-Memory Multiprocessor

multi-processor가 하나의 main memory를 사용함에 따라 여러가지 memory 일관성에 문제점이 발생하게 됩니다. memory coherent를 유지하면서 private cache를 효율적으로 다루는 방법이 없을까요?

대표적으로 snoop라는 protocol이 있습니다. 이 snoop을 통해 서로 다른 cache들이 하는 것을 옅듣고 minitor하죠.

Snoopy Cache

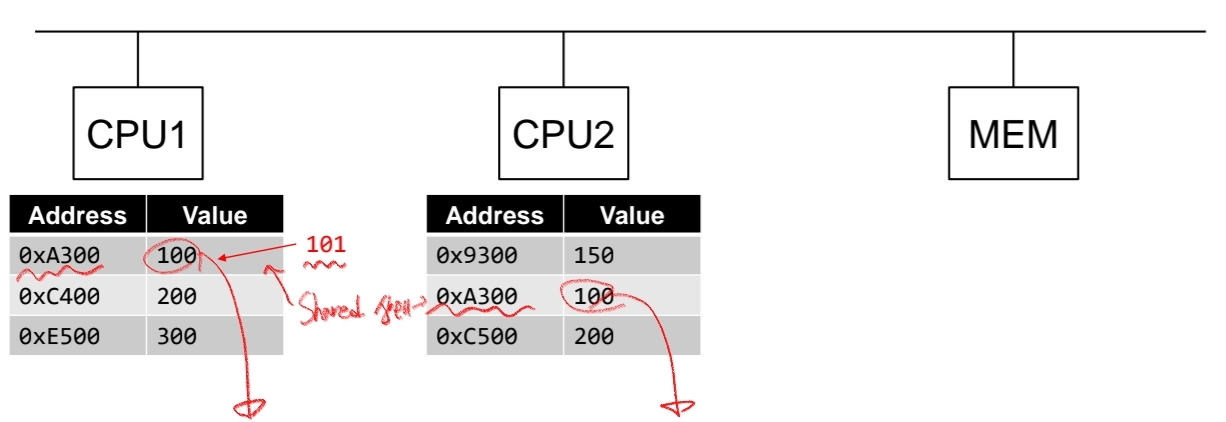

R나 W할 때 다른 cache에 intent를 보내는 것이 어떻게 보면 snoop죠. 예시를 통해 보겠습니다.

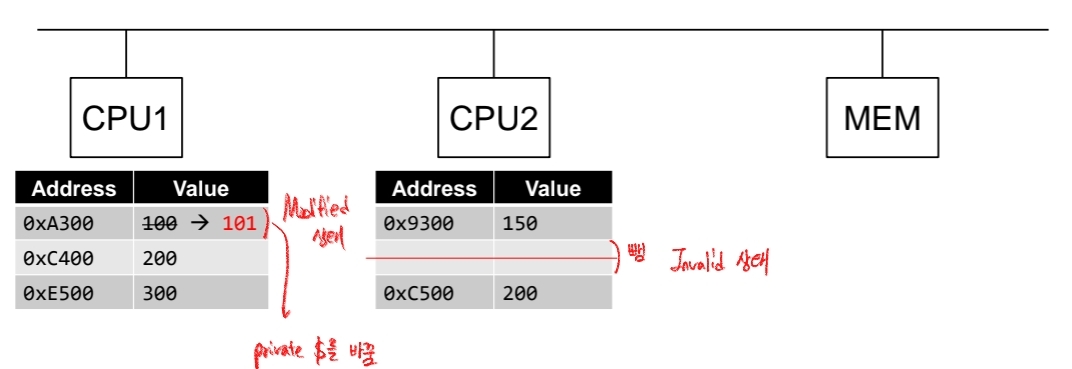

위와 같이 0xA300이라는 주소에 100이라는 value를 CPU1 cache와 CPU2 cache가 서로 가지고 있습니다. 즉, shared된 상태이죠. 하지만 이 때 CPU1에서 0xA300이라는 주소에 101을 write하고 싶어합니다.

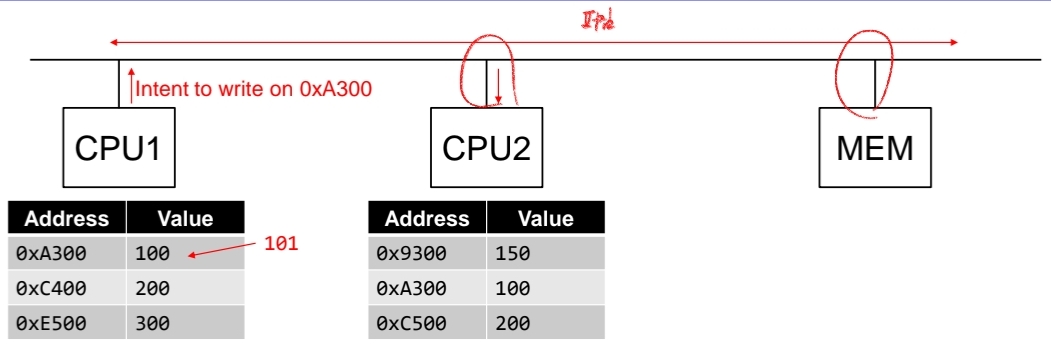

그러면 CPU1에서 0xA300에 write를 하겠다는 intent를 다른 모든 processor와 memory에 전달합니다.

그 intent를 받은 다른 CPU는 그와 같은 address를 가진 cache line을 "invalidate"상태로 만듭니다.

"Invalidate"상태로 만들었으면, CPU1은 write하고 싶었던 cache line을 modify하고 "Modified"상태로 만듭니다.

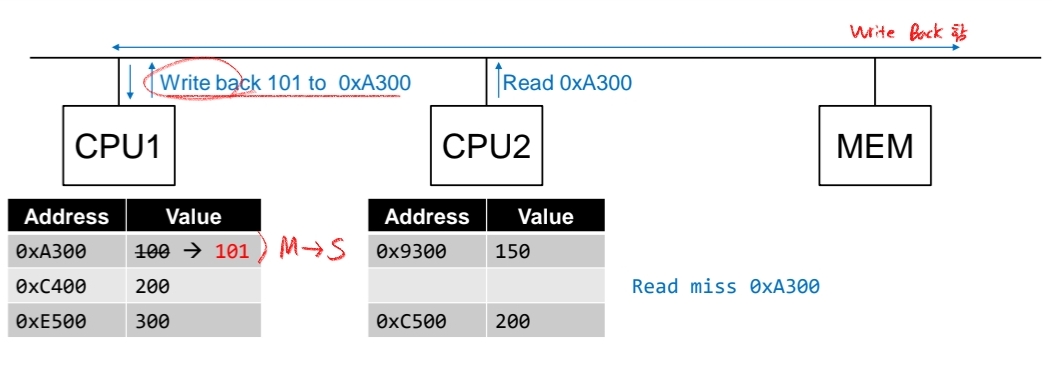

이 때 CPU2가 0xA300을 read하고 싶어합니다. 하지만 "Invalidate"상태로 인해 해당 cache line이 miss가 되죠. 그러면 마찬가지로 CPU2에서는 0xA300을 read하고 싶다는 signal을 보냅니다.

CPU1에서는 이 read 신호를 받고, memory에 write back해줍니다. 이 때, CPU1의 0xA300 cache line은 "Modified"상태에서 "Shared"상태로 변경됩니다.

이렇게 0xA300에 memory write를 진행하였으면, memory에서 0xA300을 read하여 CPU2 cache에 가져옵니다. 이렇게 해서 CPU1가 write한 주소의 value를 CPU1 cache와 CPU2 cache 둘다 수정된 value로 가지게 되는 것이죠. 동일한 주소에 같은 값을 가지게 되어 Cache Coherence가 유지된 것입니다.

위와 같은 것이 Cache Coherence의 예시입니다. Snoop 하는 과정을 통해 cache간의 value 일관성 문제를 해결했네요. 솔직히, 위 예시는 Finite State Machine을 사용했습니다. "Modified", "Shared", "Invalid"라는 상태를 사용했죠. 이 앞글자를 따와서 MSI라고 부릅니다. 다음에는 MSI와 "Exclusive"를 추가한 MESI, 여기에 "Owned"를 추가한 MOESI에 대해 알아보겠습니다.

'공부 > 컴퓨터구조' 카테고리의 다른 글

| Cache State-Transition Diagram (MESI, MOESI) (7) | 2024.04.03 |

|---|---|

| Cache State-Transition Diagram (MSI) (3) | 2024.04.03 |

| Multi-Thread (3) | 2023.12.14 |

| Out-of-Order Issue, Out-of-Order Completion (2) | 2023.12.14 |

| In-order Issue, Out-of-Order Completion (2) | 2023.12.13 |